#### EDA321: Digital Design Re-Exam - January 2014

Date: January 13, 2014

Time: 8:30-12:30

Examiner: Ioannis Sourdis

Department: Computer Science and Engineering

Inquiries: Ioannis Sourdis (extension 1744); will visit the room at **10:00** and at **11:30**

Results and grading review: See me in my office on January 31 at 10 am.

Duration: 4 hours

Grading scale: 100 points in total

Chalmers: 0: 0%-39%, 3: 40%-59%, 4: 60%-79%, 5: 80%-100% GU: Fail (U): 0%-39%, Pass (G): 40%-69%, Pass with Distinction (VG): 70%-100%

- Available references: Blank paper and a calculator are allowed. No textbooks or lecture notes, etc. allowed.

- General: Submit your solutions, in English, on blank paper sheets. Write legibly; feel free to use figures to get your point across.

The order of answering the questions does not matter (start with the easiest ones).

Please start the solutions for each problem on a new sheet. Please number the sheets so that the solutions are in numerical order.

Note that it is possible to receive partial credit for an answer even if it is not 100% correct.

Your personal identity code is required on each submitted sheet!

Good luck!

#### **Question 1: (15 points)**

a) Find the minterms of the function  $F(x0,x1,x2,x3) = \Pi(3,4,11,12,13,15)$ (2 points)

Minimize the cost of function F.

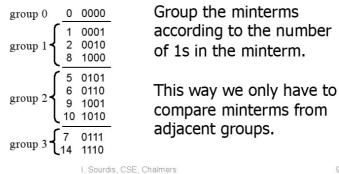

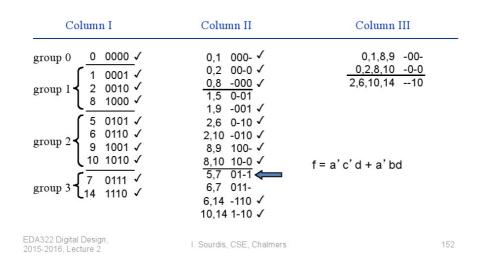

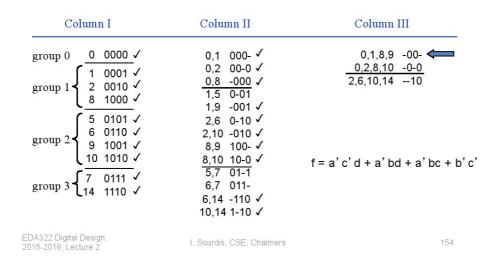

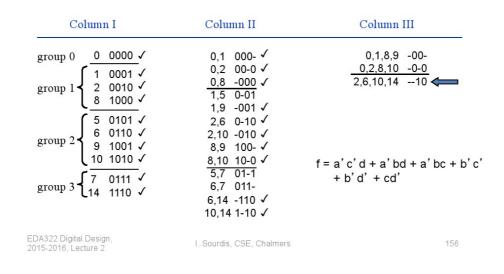

- b) Using Quine-McCluskey? (9 points)

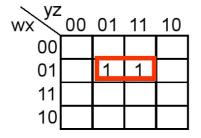

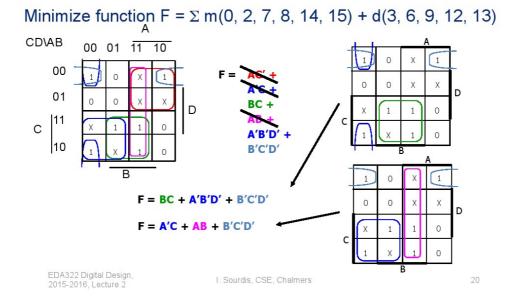

- c) using Karnaugh (4 points)

Measure the cost of the minimized function by counting the total number of 2-input gates of the circuit (e.g. a\*b + c\*d, has cost of 3).

#### Answer:

- a) similar to Lecture 2 slide 13

- b) Lecture 2 from slide 95 on

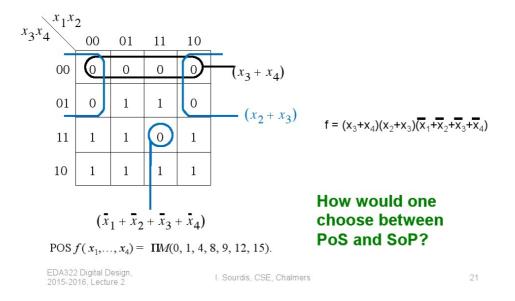

- c) similar to Lecture 2 slides 19, 20, 21

(Above mentioned lecture slides can be found at the end of this document)

#### **Question 2: (5 points)**

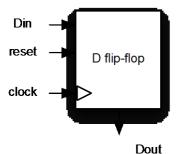

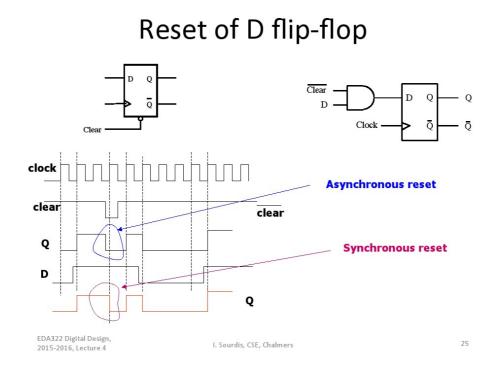

a) Describe the difference between an asynchronous and a synchronous reset in a D-flip-flop. Make a timing diagram showing the difference.

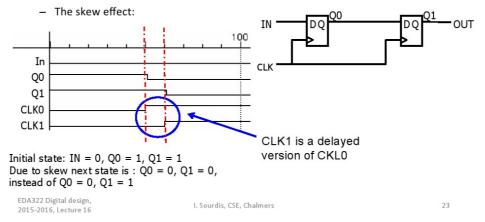

b) What is clock skew? Give an example where a clock skew may create wrong functionality of a synchronous circuit.

#### Answer:

- a) Lecture 4 slide 25

- b) Lecture 16, slide 23

(Above mentioned lecture slides can be found at the end of this document)

#### Question 3: (8 points)

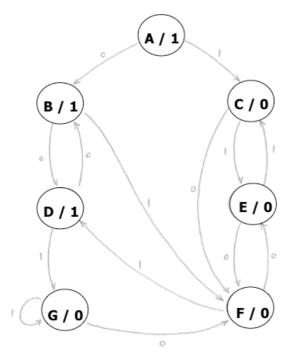

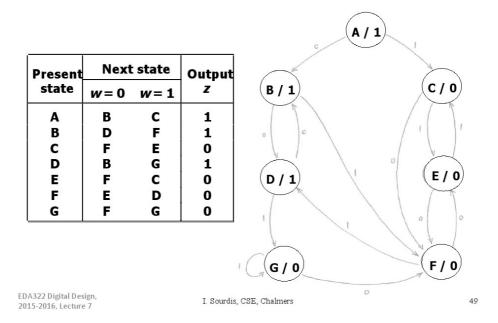

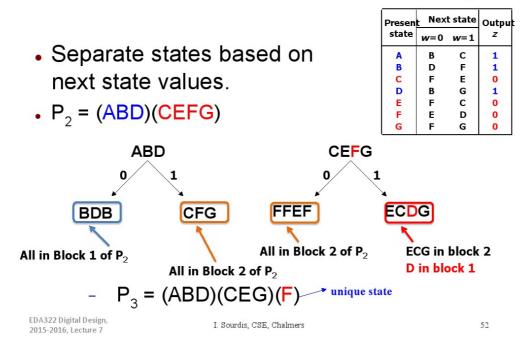

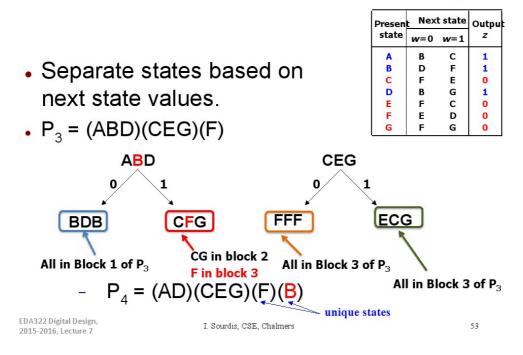

Minimize the states of the following FSM using partitioning. Draw the state diagram of the minimized FSM.

#### Answer:

a) Lecture 7 slide 49-57

(Above mentioned lecture slides can be found at the end of this document)

#### Question 4: (15 points)

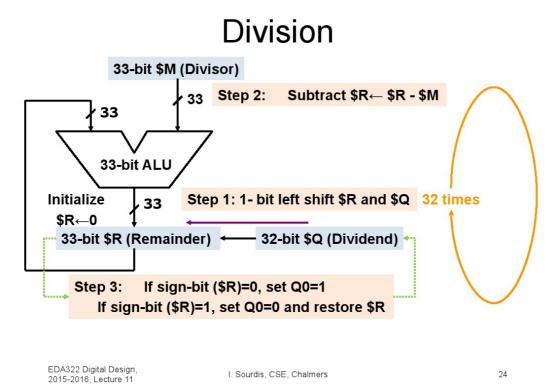

- a) Describe an unsigned binary division between a 4-bit dividend x4x3x2x1 and a 4-bit divider y4y3y2y1. Draw the block diagram and the registers used, and explain the steps needed for each iteration. How many iterations are needed for a 4 bit division? (8 points)

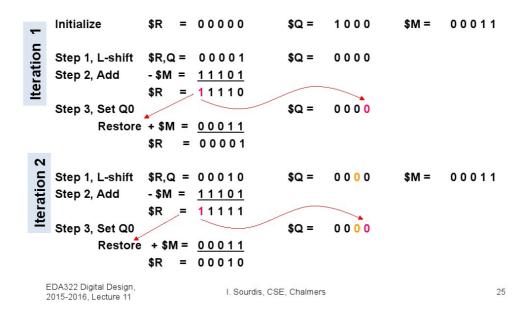

- b) Make the binary division between 8/3 showing each iteration and steps needed as you described them in (a)? (7 points)

#### Answer:

- a) Lecture 11 slide 24 (modified for 4-bits instead of 32)

- b) Lecture 11 slide 25-26

(Above mentioned lecture slides can be found at the end of this document)

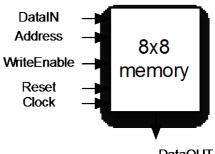

#### Question 5: (7 points)

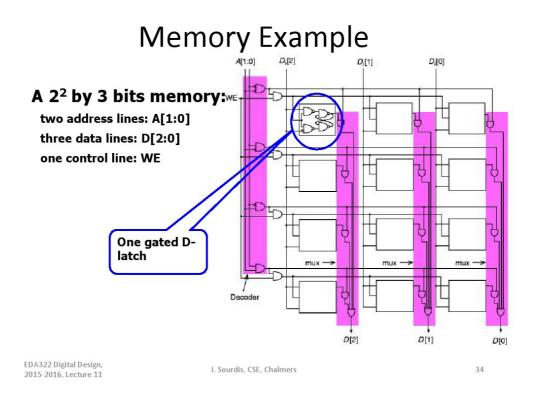

(a) (5 points)Draw the block diagram of an 8x8 memory, using as "building blocks" D flip-flops and logic gates. The memory has the following inputs:

- DataIN,

- Write-enable,

- Address

- Reset, Clock

And the following output:

• DataOUT

Note: both "DataIN" and "DataOUT" are signals of 8 bits.

-How many bits is the "Address" signal?

The D flip-flop has the following interface:

(b) (2 points)

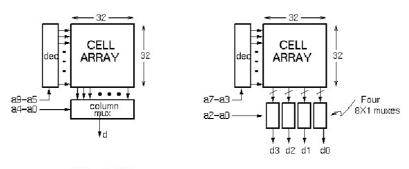

Taking the above 8x8 memory as a black box (not having the ability to change its internal design) what can we add to use it as a 64x1 memory?

#### Answer:

- a) lecture 11, slide 34 (but for 4x4 instead of 4x3)

- b) a column multiplexer as shown in lecture 11, slide 39

(Above mentioned lecture slides can be found at the end of this document)

#### Question 6: (10 points)

Considering the following Boolean functions:

- **1.**  $F_1 = A_0 A_1 A_3 + A_1 A_2 \bar{A}_3 + \bar{A}_0 \bar{A}_1 \bar{A}_2$

- **2.**  $F_2 = A_0 A_{1+} A_3 \overline{A}_2$

Map the above functions to an FPGA that has:

- a) 2-input Lookup Tables (LUT)

- b) 4-input LUTs

Draw the block diagram for each case: What is the minimum number of LUTs in each case (4 cases in total)?

Considering that a 2-input LUT has area A, a 4-input LUT has area  $4^*A$ , and each wire area A/4, what is the best LUT size (2-input LUTs or 4-input LUTs) that gives the lower area for each function?

#### Answer:

a.1: 7 LUT, 15 wires, area = 7\*A+15/4\*A=10.25\*A a.2: 1 LUT, 5 wires, area = 4\*A+5/4\*A=**5.25\*A** b.1: 3LUTs, 7 wires, area = 3\*A+7/4\*A=**4.75\*A** b.2: 1 LUT, 5 wires, area = 4\*A+5/4\*A=5.25\*A

#### Question 7: (10 points)

What is the difference between full custom ASICs and standard-cell ASICS? How each one is built and which one is expected to have better performance, lower power consumption, lower silicon area, and why?

#### Answer:

Standard cell ASICs use pre-fixed cells implementing a single gate or a flip-flip (or bigger blocks, then called block-based ASICs). Tools are then used to place and wire these standard cells. Cells are described in libraries of some vendor that the hardware designer uses.

In full-custom ASICs, every gate and flip-flop is designed in detail down to the transistor level and even lower. Full custom ASICs get better performance, lower power consumption, and better area efficiency compared to standard cell ASICs because designers can optimize them in more detail (down to the transistor level). However, they are more difficult and expensive to design. Full-custom ASICs are meant for critical blocks (e.g. blocks that cause performance bottlenecks).

#### Question 8: (10 points)

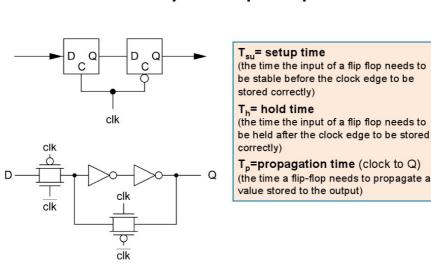

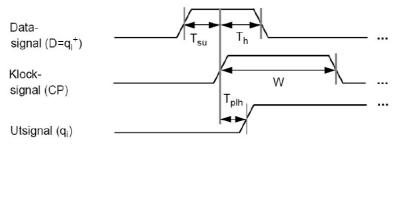

Explain the timing constraints of a D flip-flop.

- a) What is the propagation time, setup time and hold time? (6 points)

- b) Make a timing diagram to show the above time constraints in a D flip-flop. (3 points)

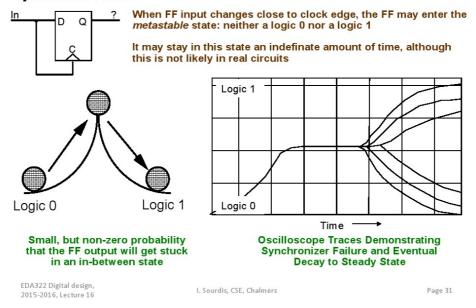

- c) Explain when a flip-flop may enter a metastable state. (3 points)

#### Answer:

Lecture 16 slides 18, 19, 31

#### Question 9: (10 points)

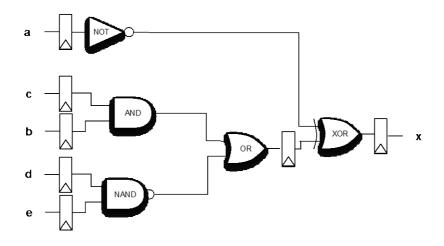

Calculate the maximum delay of the circuit (critical path delay), considering the following:

- o a NOT gate has a delay of 1 ns

- o an AND gate has a delay of 3 ns

- a NAND gate has a delay of 2 ns

- o a XOR gate has a delay of 7 ns

- $\circ$  an OR gate has a delay of 3 ns

- Propagation time (clock to output) for a flip-flop 1ns

- Setup time for a flip-flop 2ns

- Wires have zero delay

- All inputs (a, b, c, d, e) have zero delay

#### Answer:

The Critical path is from the output of the flip-flops connected to "a" to the input of the flip-flop at the output.

Max Delay = (Propagation delay of the flip-flop) + (Delay of the NOT gate) + (Delay of the XOR gate) + (Setup-time of the flip-flop) ⇔ Max Delay = 1ns + 1ns + 7ns +2ns = 11ns

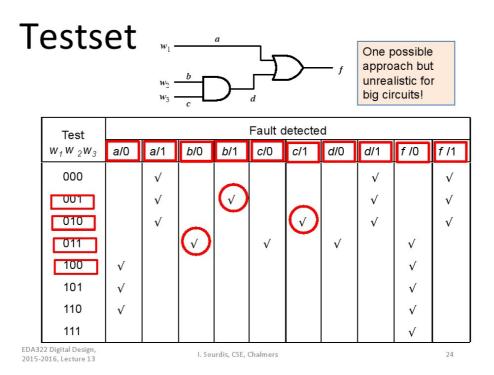

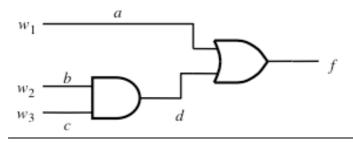

#### Question 10: (10 points)

Find the test-set of inputs that detect all the single stuck-at faults for the following circuit:

**Answer:** Lecture 13, slide 24.

END of EXAM

Lecture Slides

Question 1:

#### Conversion between canonical forms

Relation between maxterms and minterms of a function

$F(x,y,z) = \Sigma(1,3,5,6,7) = \Pi(0,2,4)$

... and for the inverted function:  $F'(x,y,z) = \Pi(1,3,5,6,7) = \Sigma(0,2,4)$

EDA322 Digital Design, 2015-2016, Lecture 2

I. Sourdis, CSE, Chalmers

Karnaugh-diagram

W'XY'Z + W'XYZ =(W'XZ)(Y'+Y) = W'XZ

Note: (Y'+Y)=1

EDA322 Digital Design, 2015-2016, Lecture 2

I. Sourdis, CSE, Chalmers

### Karnaugh of 4 variables

#### Product of Sums (maxterms)

#### 1. Find all the prime implicants

$$f(a,b,c,d) = \sum m(0,1,2,5,6,7,8,9,10,14)$$

EDA322 Digital Design 2015-2016, Lecture 2

95

| Column I                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Column II                                            | Column III                                           |     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-----|--|

| $\begin{array}{c} \text{group } 0 \\ \text{group } 1 \\ \left\{ \begin{array}{c} 0 & 0000 \\ \hline 1 & 0001 \\ 2 & 0010 \\ \hline 2 & 0010 \\ \hline 8 & 1000 \\ \hline \end{array} \right. \\ \text{group } 2 \\ \left\{ \begin{array}{c} 5 & 0101 \\ \hline 5 & 0101 \\ \hline 9 & 1001 \\ 10 & 1010 \\ \hline \end{array} \right. \\ \text{group } 3 \\ \left\{ \begin{array}{c} 7 & 0111 \\ \hline 7 & 0111 \\ 14 & 1110 \\ \end{array} \right. \\ \end{array} \right.$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$ |     |  |

| EDA322 Digital Design,<br>2015-2016, Lecture 2                                                                                                                                                                                                                                                                                                                                                                                                                               | I. Sourdis, CSE, Chalmers                            |                                                      | 149 |  |

| Column I                                              | Column II                                                                                                                                                                                                                                                                                                                                                                                                                        | Column III                                                                                                                                                                                                                                 |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{ccccccc} 0,1 & 000- \checkmark \\ 0,2 & 00-0 \checkmark \\ \hline 0,8 & -000 \checkmark \\ \hline 1,5 & 0-01 \\ 1,9 & -001 \checkmark \\ 2,6 & 0-10 \checkmark \\ 2,10 & -010 \checkmark \\ 2,10 & -010 \checkmark \\ 8,9 & 100- \checkmark \\ \hline 8,9 & 100- \checkmark \\ \hline 8,10 & 10-0 \checkmark \\ \hline 5,7 & 01-1 \\ 6,7 & 011- \\ 6,14 & -110 \checkmark \\ 10,14 & 1-10 \checkmark \end{array}$ | $\begin{array}{r} 0,1,8,9 & -00-\\ 0,2,8,10 & -0-0\\ \hline 0,0,1,9 & -00-\\ \hline 0,8,2,10 & 0.0\\ \hline 2,6,10,14 & -10\\ \hline 2,10,0,14 & -10\\ \hline 2,10,0,14 & -10\\ \hline \end{array}$ We can eliminate repeated combinations |

| EDA322 Digital Design,<br>2015-2016, Lecture 2        | I. Sourdis, CSE, Chalmers                                                                                                                                                                                                                                                                                                                                                                                                        | 150                                                                                                                                                                                                                                        |

| Column I                                              | Column II                                            | Column III                                                                                                                                               |

|-------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{r} 0,1,8,9 & -00-\\ \underline{0,2,8,10} & -0-0\\ 2,6,10,14 &10\\ \end{array}$<br>Now we form f with the terms not checked<br>f = a' c' d |

| EDA322 Digital Design,<br>2015-2016, Lecture 2        | I. Sourdis, CSE, Chalmers                            | 151                                                                                                                                                      |

| Column I                                                                                                                                                                                                                                                                                                                                                                                                        | Column II                                            | Column III                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------|

| $\begin{array}{c c} \text{group } 0 & 0 & 0000 \checkmark \\ \hline 1 & 0001 \checkmark \\ 2 & 0010 \checkmark \\ \hline 2 & 0010 \checkmark \\ 8 & 1000 \checkmark \\ \hline \\ \text{group } 2 \begin{cases} 5 & 0101 \checkmark \\ 6 & 0110 \checkmark \\ 9 & 1001 \checkmark \\ 10 & 1010 \checkmark \\ \hline \\ \text{group } 3 \begin{cases} 7 & 0111 \checkmark \\ 14 & 1110 \checkmark \\ \end{cases}$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 0,1,8,9 -00-<br>0,2,8,10 -0-0<br>2,6,10,1410<br>f = a' c' d + a' bd + a' bc |

| EDA322 Digital Design,<br>2015-2016, Lecture 2                                                                                                                                                                                                                                                                                                                                                                  | I. Sourdis, CSE, Chalmers                            | 153                                                                         |

| Column I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Column II                                            | Column III                     |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|--|--|

| $\begin{array}{c} \text{group } 0 & \underbrace{0 & 0000 } \checkmark \\ \text{group } 1 \left\{ \begin{array}{c} 1 & 0001  \checkmark \\ 2 & 0010  \checkmark \\ 8 & 1000  \checkmark \\ \end{array} \right. \\ \text{group } 2 \left\{ \begin{array}{c} 5 & 0101  \checkmark \\ 6 & 0110  \checkmark \\ 9 & 1001  \checkmark \\ 10 & 1010  \checkmark \\ \end{array} \right. \\ \text{group } 3 \left\{ \begin{array}{c} 7 & 0111  \checkmark \\ 14 & 1110  \checkmark \end{array} \right. \end{array} \right.$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | f = a'c'd + a'bd + a'bc + b'c' |  |  |

| EDA322 Digital Design,<br>2015-2016, Lecture 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I. Sourdis, CSE, Chalmers                            | 155                            |  |  |

#### **Question 2:**

### **Clock Skew**

- The Problem

- correct behavior requires that the next state of all memory elements are determined by all the memory elements thus at the same time

- This is difficult in high performance systems since the time it takes for the clock to arrive, are of the same magnitude as the delay through the logic

Question 3:

### State Minimization: Partitioning

- State Minimization through <u>Partitioning</u>:

- Form an initial partition (P<sub>1</sub>) that includes all states.

- Form a second partition (P<sub>2</sub>) by separating the states into blocks based upon their output values.

- Form a third partition  $(P_3)$  by separating the states into blocks corresponding to the next state values.

- Continue partitioning until two successive partitions are the same (i.e. P<sub>N-1</sub> = P<sub>N</sub>).

- All states in any one block are equivalent.

- Equivalent states can be combined into a single state.

EDA322 Digital Design, 2015-2016, Lecture 7

I. Sourdis, CSE, Chalmers

### State Minimization: Partitioning

| Initial Partition: |

|--------------------|

|--------------------|

| $P_1 = (ABCDEFG)$ |

|-------------------|

|-------------------|

| Present | Next state |     | Output |  |

|---------|------------|-----|--------|--|

| state   | w = 0      | w=1 | z      |  |

| Α       | В          | С   | 1      |  |

| В       | D          | F   | 1      |  |

| С       | F          | Е   | 0      |  |

| D       | В          | G   | 1      |  |

| E       | F          | С   | 0      |  |

| F       | E          | D   | 0      |  |

| G       | F          | G   | 0      |  |

The initial partition contains all states in the state diagram / table.

EDA322 Digital Design, 2015-2016, Lecture 7

I. Sourdis, CSE, Chalmers

Separate states based on output value.

-  $P_2 = (ABD)(CEFG)$

| Present | Next state |   | Output<br>z |  |

|---------|------------|---|-------------|--|

| state   | w=0 $w=1$  |   |             |  |

| Α       | В          | С | 1           |  |

| В       | D          | F | 1           |  |

| С       | F          | E | 0           |  |

| D       | В          | G | 1           |  |

| E       | F          | С | 0           |  |

| F       | E          | D | 0           |  |

| G       | F          | G | 0           |  |

EDA322 Digital Design, 2015-2016, Lecture 7

I. Sourdis, CSE, Chalmers

51

### State Minimization: Partitioning

### State Minimization: Partitioning

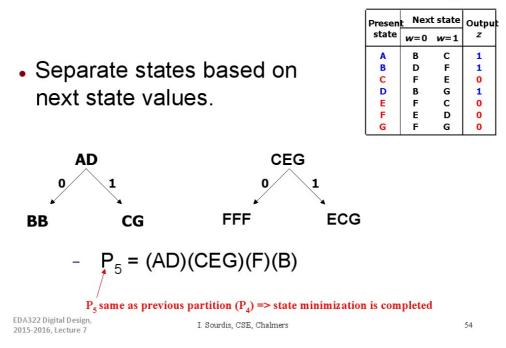

- Since P<sub>4</sub> = P<sub>5</sub>, state minimization is complete.

- The equivalent states are:

- A = D - C = E = G

- B

- F

## Thus, the FSM can be realized with just 4 states.

EDA322 Digital Design, 2015-2016, Lecture 7

I. Sourdis, CSE, Chalmers

**FSM: State Minimization**

| Present | Next  | Output |   |

|---------|-------|--------|---|

| state   | w = 0 | w = 1  | z |

| Α       | В     | С      | 1 |

| В       | Α     | F      | 1 |

| С       | F     | С      | 0 |

| F       | С     | Α      | 0 |

#### **Minimized State Table**

EDA322 Digital Design, 2015-2016, Lecture 7

I. Sourdis, CSE, Chalmers

56

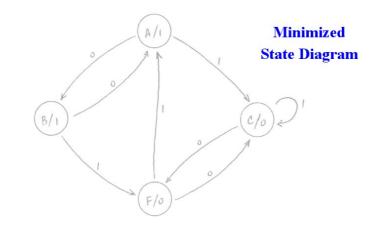

### **FSM: State Minimization**

EDA322 Digital Design, 2015-2016, Lecture 7

I. Sourdis, CSE, Chalmers

57

#### **Question 4:**

### Ex: 8/3 = 2, Remainder = 2

### Ex: 8/3 = 2 (Remainder = 2) (Con'd)

|                                                                 |                                                                      | \$R =                       | 00010                                    | \$Q =       | 0000                | \$M =     | 00011 |

|-----------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------|------------------------------------------|-------------|---------------------|-----------|-------|

| tion 3                                                          | Step 1, L-shift<br>Step 2, Add                                       | \$R,Q=<br>-\$M =            | 00100<br>11101                           | \$Q =       | 0000                | \$M =     | 00011 |

| lteration                                                       | Step 3, Set Q0                                                       |                             | 00001                                    | \$Q =       | 0001                |           |       |

| Iteration 4                                                     | Step 1, L-shift<br>Step 2, Add                                       | \$R,Q =<br>- \$M =<br>\$R = |                                          | \$Q =       | 0010                | \$M =     | 00011 |

| Itera                                                           | Step 3, Set Q0<br>Restore                                            |                             | 00011                                    | \$Q =       | 0 0 1 <b>0</b> Fina | l quotiei | nt    |

| \$R = 00010 <i>Remainder</i>                                    |                                                                      |                             |                                          |             |                     |           |       |

| Note "Restore \$R" in Steps 1, 2 and 4. This method is known as |                                                                      |                             |                                          |             |                     |           |       |

| the RESTORING DIVISION. An improved method, NON-RESTORING       |                                                                      |                             |                                          |             |                     |           |       |

|                                                                 | DIVISION, is poss<br>EDA322 Digital Design,<br>2015-2016, Lecture 11 | sible (Ha                   | <b>macher, et al.)</b><br>I. Sourdis, CS | SE, Chalmei | rs                  |           | :     |

2015-2016, Lecture 11

#### **Question 5:**

### Column MUX in ROMs and RAMs:

- Controls physical aspect ratio

- In DRAM, allows reuse of chip address pins

1K X 1 ROM

EDA322 Digital Design, 2015-2016, Lecture 11

I. Sourdis, CSE, Chalmers

Page 39

#### **Delay in Flip-flops**

EDA322 Digital design, 2015-2016, Lecture 16

I. Sourdis, CSE, Chalmers

Page 18

# Time parameters for clocked memory elements

EDA322 Digital design, 2015-2016, Lecture 16

I. Sourdis, CSE, Chalmers

### Metastability and Asynchronous Inputs

Synchronizer Failure

**Question 10:**